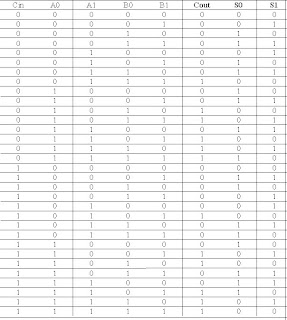

El código en VHDL no lo pongo, es muy sencillo de hacer, sólo tienes que poner como variable de selección al carry de entrada, de ahí te vas haciendo caso por caso, hasta que cumplas las 32 combinaciones algo sencillo, no?

El código en VHDL no lo pongo, es muy sencillo de hacer, sólo tienes que poner como variable de selección al carry de entrada, de ahí te vas haciendo caso por caso, hasta que cumplas las 32 combinaciones algo sencillo, no?library IEEE ;

use IEEE.std_logic_1164.all;

entity sumador_restador is

port(

A,B : in std_logic_vector(1 downto 0);

Ci : in std_logic;

X : in std_logic; ---Selector de operación

S : out std_logic_vector(1 downto 0);

Co : out std_logic

);

end sumador_restador;

architecture recurrente of sumador_restador is

signal C :std_logic_vector(2 downto 0); --Acarreos intermedios

signal P :std_logic_vector(1 downto 0); --Complemento de B

signal V :std_logic_vector(1 downto 0); --Inversion

begin

process(A,B,Ci,X,P,V)

begin

V<=(others=> X); --Vector X de 2 bits

P<= B XOR V; --Complemento a dos

C(0)<= Ci XOR X;

FOR i IN 0 TO 1 loop

S(i)<=(A(i) XOR P(i)) XOR C(i); --Suma recurrente

C(i+1)<= ((A(i) AND P(i)) OR (A(i) AND C(i))) OR (P(i) AND C(i)); --Acarreo recurrente

end loop;

end process;

Co<= C(2);

end recurrente;

library IEEE ;

use IEEE.std_logic_1164.all;

entity sumador_restador is

port(

A,B : in std_logic_vector(1 downto 0);

Ci : in std_logic;

x : in std_logic; ---Selector de operación Sumador '0'/ Restador '1'

S : out std_logic_vector(2 downto 0);

Co : out std_logic -- Sumador/Restador '0'

);

end sumador_restador;

architecture recurrente of sumador_restador is

begin

process (A,B,Ci,x)

begin

co <= (A(0) and A(1) and (not (B(1))) and ci)OR

(A(0) and (not (B(0))) and (not (B(1))) and x ) OR

(A(0) and A(1) and B(0) and (not (ci))) OR

(A(1) and (not (B(0))) and (not (ci)) and x) OR

(A(0) and (not(B(1))) and (not(ci)) and x) OR

((not (B(0))) and (not (B(1))) and (not (ci)) and x)OR

(B(0) and B(1) and ci and (not (x))) OR

(A(1) and B(0) and ci and (not (x))) OR

(A(0) and B(1) and ci and (not (x))) OR

(A(0) and B(0) and B(1) and (not (x))) OR

(A(1) and (not (B(1))) and x) OR

(A(1) and B(1) and (not (x)));

s(0)<= (a(0) and b(0) and ci) OR

((not (a(0))) and (not(b(0))) and ci) OR

((not(a(0))) and b(0) and (not(ci))) OR

(a(0) and (not(b(0))) and (not(ci)));

s(1) <= ((not(a(0))) and a(1) and b(1) and ci and x) OR

((not (a(0))) and a(1) and b(0) and b(1) and x) OR

(a(0) and (not (a(1))) and (not(b(0))) and b(1) and x) OR

((not(a(0))) and (not(a(1))) and (not(b(1))) and ci and x) OR

((not(a(0))) and (not(a(1))) and b(0) and (not(b(1))) and x) OR

(a(0) and a(1) and (not(b(0))) and (not(b(1))) and x) OR

(a(0) and (not(a(1))) and b(1) and (not(ci)) and x) OR

(a(0) and a(1) and (not(b(1))) and (not(ci)) and x) OR

(a(0) and a(1) and b(1) and ci and (not(x))) OR

(a(0) and a(1) and b(0) and b(1) and (not(x))) OR

((not(a(0))) and (not(a(1))) and (not(b(0))) and b(1) and (not(x))) OR

(a(0) and (not(a(1))) and (not(b(1))) and ci and (not(x))) OR

(a(0) and (not(a(1))) and b(0) and (not(b(1))) and (not(x))) OR

((not(a(0))) and a(1) and (not(b(0))) and (not(b(1))) and (not(x))) OR

((not(a(0))) and (not(a(1))) and b(1) and (not(ci)) and (not(x))) OR

((not(a(0))) and a(1) and (not(b(1))) and (not(ci)) and (not(x)));

s(2) <= (a(1) and b(0) and b(1) and ci) OR

((not(a(1))) and b(0) and (not(b(1))) and ci) OR

((not(a(1))) and (not(b(0))) and b(1) and (not(ci))) OR

(a(1) and (not(b(0))) and (not(b(1))) and (not(ci)));

end process;

end recurrente;